- Qualcomm Launches Snapdragon 4 Gen 2 Mobile Platform

- AMD Launches Ryzen PRO 7000 Series Mobile & Desktop Platform

- Intel Launches Sleek Single-Slot Arc Pro A60 Workstation Graphics Card

- NVIDIA Announces Latest Ada Lovelace Additions: GeForce RTX 4060 Ti & RTX 4060

- Maxon Redshift With AMD Radeon GPU Rendering Support Now Available

Intel CPU Architecture ‘Could Scale to 1,000 Cores’

Ten years ago, the thought of a dual-core CPU didn’t quite compute (pun intended) in our minds, because such products simply didn’t exist. But today, multi-core processors are common in even the simplest of mobile devices, and on our desktops, some are lucky enough to have six cores at their disposal. For the most part, today’s CPUs offer a great amount of power for most people, but what about the future?

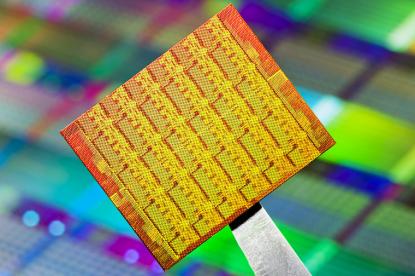

Intel’s been an innovator in multi-core technologies, having shown off CPU prototypes with models featuring 48 or more cores. Generally, each one of these cores isn’t quite as full-featured as a core on a regular desktop CPU, but with the right types of scenarios, many cores can mean many times faster. Take a look at GPUs, for example. They feature many cores and given the right task, can leave a CPU in the dust.

With Intel’s current in-progress architectures, the company is confident that its designs could scale up to 1,000 cores on a single chip without issue. It seems lofty, but being that GPU vendors already pack many cores into a single chip, Intel should be able to, too. It mentions, though, that after 1,000, the diameter of the “mesh” (the network connecting the cores) would reach a point where it would see diminishing returns. Nothing says that future innovations wouldn’t correct this, however.

Adding many cores to a single chip adds a lot of complexity, and one of the reasons GPU vendors can get away with it is that the cores are simpler in design and have more fixed functions. Intel suggests that one ideal solution to prevent issues would be to remove the cache coherency of the cores, but that’s something not likely to happen too soon.

The thought of a 1,000 core CPU is drool-worthy to say the least, and would be a highly sought-out by those who manage super-computers or the beefiest of servers. I’m sure it also would play a mighty game of Solitaire as well! *dreams*

The novelty of this processor is in its tiled architecture and the network and address infrastructure. Each core has a “mesh interface component” that packages data into packets and connects to an on-board router. Each tile also has a “message-passing buffer,” with 16 kilobytes of random access memory. The team has tried various approaches to streamline the ability of the processor to pass messages among the many cores.